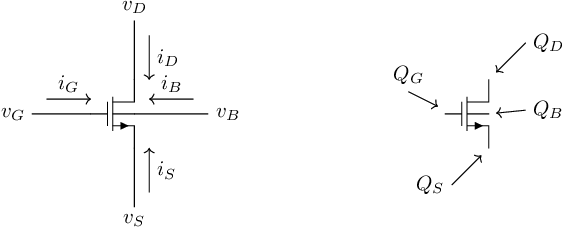

The vast majority of transistor models define terminal currents and terminal charges as shown in Figure 8.

Being inherently a four-terminal device, four generic equations for the current follow:

and four generic equations for terminal charge follow:

Small-signal wise this leads to 16 transconductances

|

|

and leads to 16 transcapacitances

|

|

These gxy and cxy can be collected in 16 Y-parameters as Yxy = gxy + jωcxy.

Note that no properties, no currents, nothing in the behavior of a transistor change if all terminal voltages are changed by an arbitrary ΔV . Offsetting all terminal voltages by the same amount effectively only means that your reference voltage is changed. And your transistor does not care what you assume as reference potential. This implies that:

The fact that adding the same voltage to all nodes does not change the behavior of the transistor in any way, implies that the sum of some transcapacitances and transconductances is zero:

while the laws of conservation of charge enforce other sums to zero:

The fact that these sums equal zero implies that a number of the 16 transcapacitances and

transconductances have negative values.

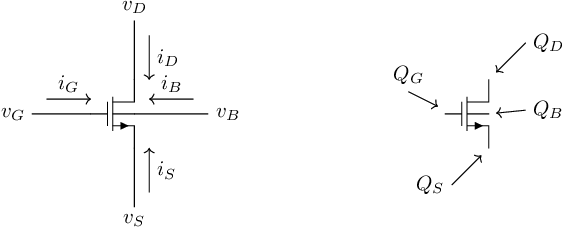

Although e.g. negative transcapacitances may seem weird at first sight, it only means that the charge at some node decreases if the voltage at one of the (other) nodes increases. To illustrate that this is normal behavior of even passive (linear, two terminal) devices, the example below assumes a regular capacitor.

Applying voltages vt and vb to the top plate and bottom plate respectively, charge accumulates on the top plate (indicated by “t”) and on the bottom plate (indicated by “b”) as

which leads to

It may be clear that in this set of four transcapacitances — associated with a straight-forward linear capacitor — also shows the redundancy properties and the summing-to-zero properties that were described above. Using those, we usually describe the linear capacitor by its ctt = C or by its cbb = C in hand derivations and manual calculations. Similar results follow for two-terminal resistive component, or for any generic 2 terminal device for that matter. Moreover, devices with more-than-2 ports are merely extensions of the 2-terminal devices.

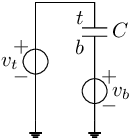

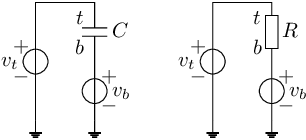

For a device with 2 terminals, the laws of conservation of charge (per unit time for currents) dictates a very simple symmetry. For e.g. resistors and capacitors

it can readily be derived that the transcapacitances respectively transconductances are:

For two-terminal devices, gxy = gyx and cxy = cyx.

For devices with more than 2 terminals, in general gxy≠gyx and cxy≠cyx. For example a transcapacitance cgd in general is not equal to cdg: the change in (here) gate charge qG(V D,V G,V S,V B) due to a drain voltage change can be completely different from the change in drain charge qD(V D,V G,V S,V B) due to a gate voltage change. The same holds of course any transcapacitance cxy and cyx for all x≠y, and for any gxy and gyx for all x≠y: in general they are not identical. Only in special cases — like 2-terminal devices — they have to be identical.